如今,电子产品的高度集成化与小型化,使得芯片容易过热,这成为电子产品的“隐形杀手”。同时,芯片面临严峻的散热挑战:芯片制程越精细,热流密度就越大,热设计功耗就越高,芯片性能制约就越严重,高效热管理成为制约芯片性能释放的瓶颈。

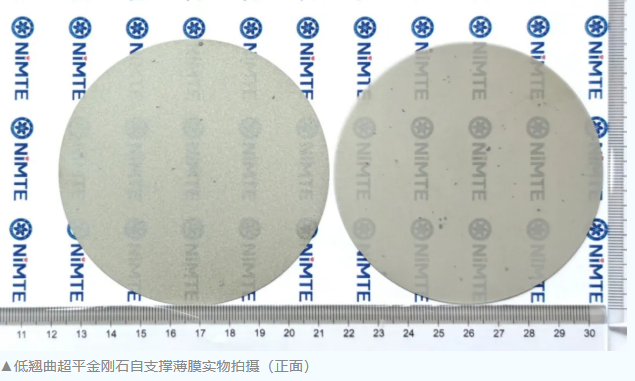

近日,中国科学院宁波材料技术与工程研究所(以下简称“宁波材料所”)科研团队,成功制备出4英寸超薄超平金刚石自支撑薄膜,为克服长期制约芯片键合制程的翘曲难题、推动金刚石在芯片热管理领域的发展,迈出重要一步。

▲低翘曲超平金刚石自支撑薄膜实物拍摄(正面)

01金刚石散热 理想材料的现实瓶颈

芯片在使用过程中,当内部产生的热量无法有效散发时,局部区域会形成“热点”,导致芯片性能下降,甚至硬件损坏。超过半数的设备故障与过热直接相关。

特别是碳化硅、氮化镓等第三代半导体芯片,当它们在高频大功率工作环境下“高强度工作”时,会产生高热流密度,这让“通过降低壳体-环境热阻”的传统散热方案难以为继。

金刚石是天生的“散热冠军”——它的热导率超过2000W/m·K,是铜的5倍以上。

如果把芯片直接“粘”在金刚石衬底上,能大大降低“近结热阻”(芯片发热核心到散热材料之间的热量传递阻力)和“结温”(芯片内部最关键的发热点温度),就像给芯片核心贴了个“超导冰袋”,这也被视为未来高性能芯片及3D封装热管理的理想方案。

但金刚石薄膜是在其他衬底上“长”出来的,金刚石与衬底间的本征热膨胀系数差异及形核、生长工艺适配性问题,导致剥离衬底后的金刚石薄膜翘曲严重,无法满足芯片键合工艺对衬底超高平坦度的严苛要求。

这让金刚石的散热潜力一直被“封印”。解决衬底翘曲问题是金刚石薄膜应用于芯片键合的关键。

02 工艺创新与突破 打通金刚石芯片键合制程通道

宁波材料所研究团队基于自主设计开发的915MHz-75kW微波等离子体化学气相沉积(MPCVD)设备,通过技术创新与工艺优化,成功制备出4英寸金刚石自支撑薄膜,薄膜厚度小于100μm。

该薄膜在自支撑状态下,翘曲度可稳定控制在10μm以内,比常规工艺制备的金刚石薄膜降低一个数量级。

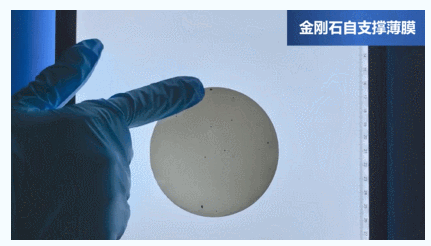

最关键的是,这种超低翘曲度赋予金刚石薄膜超乎寻常的平坦特性,使其能在无外力作用下自发贴附于玻璃基板,展现出独特的“自吸附”现象。

超薄的自支撑结构为封装设计带来了更高的灵活性与多维设计自由度,在半导体芯片异质集成与3D堆叠等先进封装工艺中展现出巨大应用潜力。

目前,研究团队正在为开发出6英寸以上更大尺寸的超薄、超低应力金刚石导热材料而奋斗,持续推进和拓展其在AI、射频等高功率芯片热管理领域的应用。

手机资讯

手机资讯 官方微信

官方微信

豫公网安备41019702003646号

豫公网安备41019702003646号